RISC-V

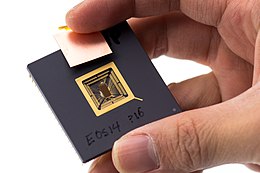

RISC-V Processore prototipo che utilizza l'architettura RISC-V nel gennaio 2013

Processore prototipo che utilizza l'architettura RISC-V nel gennaio 2013

| Tipo | RISC ISA , progetto , set di istruzioni , piattaforma IT |

|---|---|

| Sito web | riscv.org |

RISC-V (pronunciato in inglese "RISC five" che significa "cinque RISC") è un'architettura del set di istruzioni (architettura del set di istruzioni ISA) RISC aperto e gratuito , che include 32, 64 e 128 bit, ovvero specifiche aperte che possono essere utilizzati liberamente dall'istruzione, dalla ricerca e dall'industria. È implementato in diversi SoC , destinati all'on -board, oggetti connessi (supportati da diversi sistemi real-time o per l'on-board, come Arduino , FreeRTOS , HarmonyOS , LiteOS , RT-Thread , RustOS , Zephyr .. . ), computer leggeri sotto forma di SBC , generalmente con Linux ( Debian , Fedora , Ubuntu , Yocto ) o anche varianti di OpenWrt , server e un progetto europeo avviato nel 2019, si propone di utilizzarlo nei supercomputer domestici come acceleratori entro bassi -power SoC sviluppati localmente e funzionanti sotto GNU/Linux , come la stragrande maggioranza dei supercomputer.

motivazioni

Questo progetto, inizialmente creato nella divisione di informatica dell'Università della California a Berkeley , USA , era inizialmente destinato allo studio e alla ricerca, ma è diventato di fatto uno standard per l'architettura aperta nel settore.

L'obiettivo di questo progetto è quello di creare uno standard aperto di set di istruzioni per microprocessori, come lo standard TCP / IP per le reti o UNIX per i sistemi operativi, l'architettura dei processori è per il momento sempre chiusa, limitando il progresso, le implementazioni o il supporto nei sistemi operativi .

Storico

Il design del processore inizia nel 2010 presso l'University of California, Berkeley, al fine di sviluppare un processore con la conoscenza del XXI ° secolo , non avendo alla compatibilità trascina con vecchie architetture 20 anni come ARM o Intel x86 architettura e allo stesso tempo desiderando che l' architettura del set di istruzioni del processore (ISA) rimanga aperta.

Nel 2014 è stata pubblicata la versione 2.0 delle specifiche, diversi importanti produttori erano interessati al progetto.

Nel 2015 è stata creata la fondazione RISC-V con più di 100 membri e un consiglio di amministrazione composto da aziende come Google , Nvidia , Western Digital , NXP Semiconductors , Microsemi e Bluespec , nonché rappresentanti dell'Università di Berkeley. Da allora, aziende come AMD , Qualcomm e IBM si sono unite.

Nel 2016, Nvidia prevede di utilizzare un microcontrollore RISC-V per le sue GPU e prevede quindi di triplicare le sue prestazioni rispetto al proprio microcontrollore, Falcon. Il Falcon è anche un processore con architettura RISC, ma con un indirizzamento limitato a 32 bit e nessuna protezione dei thread e con i suoi limiti. Nvidia vuole quindi sostituirlo con la versione a 64 bit di RISC-V, beneficiando così dell'indirizzamento a 64 bit, delle correzioni degli errori, di un set di istruzioni espandibile e di una maggiore sicurezza.

Nel 2017 è stata rilasciata la versione 2.2 delle specifiche. Mozilla annuncia che il suo linguaggio Rust può essere compilato sull'architettura RISC-V. Il produttore di dischi rigidi, Western Digital, annuncia che consegnerà miliardi delle sue apparecchiature, con un'architettura di controller RISC-V.

il 9 luglio 2018, parte del management della società ARM decide di creare un sito denominato “riscv-basics.com” contro RISC-V, sentendo minacciato il suo mercato, in particolare, perché una parte significativa dei suoi maggiori clienti (sopra menzionati), è anche iniziando a sviluppare soluzioni basate su RISC-V. Questa azione ha fatto arrabbiare lo staff tecnico dell'azienda che l'ha vista come un attacco al movimento open source. Ha anche l'effetto di sensibilizzare un po' di più su RISC-V e creare una maggiore consapevolezza che si tratta di una valida alternativa. La direzione di ARM decide infine di chiudere il sito il giorno successivo, il10 luglio 2018.

Nel 2019, il governo americano di Donald Trump , fa pressione sui fondatori della microelettronica, come la taiwanese TSMC , la più importante al mondo, per trasferirsi in suolo americano, cosa che quest'ultima rifiuta, il tutto minacciando chi continuerebbe a lavorare con aziende cinesi come Huawei . A seguito dei rischi politici di queste pressioni, la Fondazione ha deciso di stabilirsi in un Paese neutrale: la Svizzera .

Nel ottobre 2019, Nvidia è alla ricerca di specialisti RISC-V per integrarlo come processore all'interno dei suoi SoC Tegra .

Nel ottobre 2020, Huawei rilascia i suoi primi kit di sviluppo hardware e software per i suoi nuovi microcontrollori interni, utilizzano un compilatore verso l'architettura RISC-V.

Nel luglio 2021, Haiku è portato su RISC-V, Debian Bulleseye feature freeze per il rilascio della prima versione della distribuzione a supportare ufficialmente RISC-V. Il driver grafico Radeon HD per Linux gira su architettura.

Specifiche

Implementa un set di istruzioni RISC, senza microcodice , né overlay di architettura del tipo esecuzione nel disordine o nell'ordine, o il supporto di un tipo di materiale in particolare ( ASIC , FPGA …), ma quelli -ci possono essere implementati con tutte le loro funzioni.

- Revisione 2008 dello standard IEEE-754 per l'unità di calcolo dei numeri in virgola mobile .

- Indirizzamento a 32, 64 o 128 bit.

- Possibilità per ogni implementazione di fornire istruzioni estese.

- Supporto per implementazione multicore altamente parallela e architettura multiprocessore eterogenea.

- Istruzioni di lunghezza variabile opzionali, che consentono sia di aumentare lo spazio di codifica delle istruzioni disponibile, ma anche di rendere le istruzioni più dense per migliorare le prestazioni, ridurre le dimensioni del codice statico e l'efficienza energetica.

- Un'architettura completamente virtualizzabile per facilitare lo sviluppo dell'hypervisor .

I ricercatori della University of California , Berkeley , hanno sviluppato anche una versione chiamata BOOM, l'aggiunta di out-of-order esecuzione delle istruzioni del modello RV64G.

Nomenclatura delle estensioni Extension

Il nome del processore ha un significato:

- La base è composta da RV (per RISC-V), poi 32, 64 o 128, a seconda del numero di bit, e infine, una I o una E (embedded, cioè embedded).

I possibili nomi di base sono quindi:

- RV32I

- RV32E (a bordo)

- RV64I

- RV128I

Il nome del processore è seguito da una o più lettere che descrivono le estensioni che vengono aggiunte al database:

- M - Estensione standard M ultiplicazioni e intere divisioni;

- A - L'estensione dell'istruzione standard ha tomiques ;

- F - Estensione f standard in virgola mobile a precisione singola (32 bit);

- D - norma virgola mobile estensione d precisione ouble (64 bit);

- G - G enerale, scorciatoia per le istruzioni di base, e le serie di istruzioni di cui sopra, vale a dire M, A, F, D)

- Q - standard q uadruple precisione (128 bit) floating point estensione ;

- L - estensione in virgola mobile standard, decimato il ;

- C - Istruzioni standard Extension c ompressées;

- B - Manipolazione standard Estensione b ict;

- J - Estensione standard dei linguaggi tradotti dinamicamente ( Compilation on the fly , J ust in time o JIT), riguarda linguaggi di scripting come C# , Haskell , Java , JavaScript , Lua , OCaml , PHP , Python , R , Ruby , Scala , WebAssembly , ecc;

- T - Estensione memoria standard t ransactionnelle;

- P - Istruzioni Standard Extension SIMD com p svalutato ( P acked SIMD );

- V-Standard Estensione delle operazioni v ectorielles ;

- N - estensione standard I n utente terruptions;

- S - estensione standard di S upervisor ;

- H - standard H ypervisor estensione , simili a S, ma a partire da una S.

ISA di base a 32 bit

Il set di istruzioni di base è composto da 47 istruzioni, incluse otto istruzioni di sistema ( chiamate di sistema , contatori di esecuzione), il resto è suddiviso nelle categorie calcolo, controllo di flusso e accesso alla memoria.

la versione RV32I ha 32 registri generali a 32 bit, mentre la versione RV32E (on-board, embedded ) ha solo 16 registri generali a 32 bit. Entrambi hanno anche un registro PC.

Istruzioni per il calcoloTutte le istruzioni di calcolo utilizzano tre operandi, tranne luie auipcche ne hanno solo due (un registro di destinazione e un valore immediato). Il primo operando è il registro di destinazione, il secondo il registro sorgente e il terzo, un secondo registro o un valore immediato (specificato da a inel mnemonico dell'istruzione, salvo che auipcabbia un altro significato) (le istruzioni di moltiplicazione e gli interi di divisione sono contenuti in estensione M):

- add, addi, sub : Addizione e sottrazione addi si usa con un valore immediato negativo alla sottrazione di un valore immediato.

- sll, slli, srl, srli, sra, srai : Un po 'po' di spostamento ( s hift ) + Sinistra / Destra ( en), la logica ( l ogical ) o aritmetica ( un rithmetic ).

- and, andi, or, ori, xor, xori : Operazioni logiche Bitwise inclusi e ( e ), o ( oro ) e OR esclusivo ( XOR ).

- slt, slti, sltu, sltui, ( S and if the ess t han ) imposta il registro di destinazione su 1 se il primo operando sorgente è uguale o inferiore al secondo. Il unsigned u significante ( u nsigned ). Gli operandi immediati sono limitati a 12 bit.

- lui, Carica la parte più significativa immediata ( l oad u pper i mmediate ), cioè bit 12 a 31 del registro di destinazione con un valore immediato 20 bit. Deve essere utilizzato addicon un valore immediato a 12 bit, per completare il valore.

- auipcaggiunge il valore immediato ai 20 bit più significativi del contatore ordinale (PC), deve essere utilizzato anche addiper i 12 bit meno significativi

Istruzione di ramificazione condizionale:

- beq, bne, blt, bltu, bge, bgeu, Instruction ramo ( b ranch ) condizionale per due operatori, uguali ( e qual ), diverso ( n ot e qual ), minore ( l'ittler t han ), maggiore o uguale ( g reater oro e qual ) , firmato (default) o meno ( u nsigned ).

Connessioni incondizionate:

- jal( J UMP un nd l inchiostro ), passa il controllo al indirizzo del PC a cui si aggiunge il valore con segno a 20 bit immediatamente disponibile. Aggiunge l'indirizzo dell'istruzione successiva (indirizzo di ritorno alla fine della funzione richiamata) nel registro di destinazione.

- jalr( J UMP un nd l inchiostro, r egister ), l'indirizzo interno è calcolato sommando registro sorgente ed il valore immediato a 12 bit, e l'indirizzo di istruzione viene caricato nella destinazione. Se questa istruzione è preceduta da un comando auipc, il salto può essere eseguito nell'intero spazio di memoria a 32 bit.

Le istruzioni di accesso alla memoria vengono utilizzate per trasferire i dati tra un registro e la memoria. Il primo operando è il registro, il secondo un registro contenente l'indirizzo, il terzo un valore con segno immediato a 12 bit aggiunto al contenuto del registro utilizzato per l'indirizzamento, per determinare l'indirizzo finale:

- lb, lbu, lh, lhu, lw, Caricare ( l oad ) un byte ( b yte ), halfword ( h alf-word , 16-bit) o word ( w ord , 32 bit) dalla memoria di un registro di destinazione. Le istruzioni sono estese dal segno (default) o da zeri ( u nsigned ).

- sb, sh, sw, Bagagli ( s toro ), un byte ( b yte ), halfword ( h alf-word , 16-bit) o word ( w ord , 32 bit) alla memoria.

- fence, forza la schedulazione dell'accesso alla memoria in un contesto multithread, in particolare garantendo la consistenza delle cache.

- fence.i, permette di garantire che le operazioni dalla memorizzazione alle memorie istruzioni (ad esempio la cache delle istruzioni) siano completate prima della loro esecuzione. Viene utilizzato principalmente nel caso di codice automodificato.

Un'istruzione viene utilizzata per richiamare una chiamata di sistema e un'altra imposta un punto di interruzione per il debugger :

- ecall, chiamata di sistema

- break, aggiungendo un punto di interruzione.

Sei istruzioni vengono utilizzate per leggere e scrivere nei registri di controllo e di stato del sistema (registri di controllo e di stato CSR). Il registro CSR viene letto in un registro generale, quindi aggiornato atomicamente:

- csrrw, csrrwi, csrrc, csrrci, csrrs, csrrsi,

I seguenti 6 registri CSR a 32 bit (corrispondenti a 3 valori a 64 bit, di contatori di esecuzione) sono definiti di sola lettura:

- cycle, cycleh, Clock del contatore di cicli trascorsi da un tempo di riferimento. Questo tempo può variare se è attiva la modalità di ridimensionamento dinamico della tensione e della frequenza (DVFS);

- time, timeh, Contatore in tempo reale trascorso da un tempo di riferimento (tipicamente, avvio del sistema);

- instret, instrethContatore delle istruzioni del processore eseguito ( inst ruction ret ired ).

ISA a 64 bit di base

L'ISA a 64 bit estende i registri e lo spazio di indirizzamento da 32 bit a 64 bit (XLEN = 64). Le istruzioni con il suffisso W ( inglese : W ord , che significa parola ), indicano che la loro azione è limitata a una parola (32 bit) e non riguarda i 32 bit superiori degli ingressi. Il bit di firma viene spostato al 64 ° bit (bit 63) dei registri, quindi è importante utilizzare le funzioni specializzate quando si utilizzano dati a 32 bit.

Ciò ha anche implicazioni per le operazioni immediate. Ad esempio, l'operazione di addizione immediata addi utilizzando un valore immediato di 12 bit, addiw ignora gli overflow di 32 bit e posiziona il bit di segno sul bit 63 dei registri.

ISA di base a 128 bit

Estensione vettoriale

L'estensione del vettore ha tre variabili, ELEN (numero di bit di un elemento), VLEN (numero di bit di un vettore) e SLEN (distanza di (stripping) tra due elementi) che devono essere tutte una potenza di 2 .

Comprende 32 registri vettoriali denominati da v0 a v31, è possibile raggrupparne due in quello che viene chiamato gruppo di registri vettoriali ( gruppo di registri vettoriali ) per migliorare la precisione o migliorare le prestazioni. Ci sono anche sei registri di controllo e stato ( CSR) (vstart, vxsat, vxrm, vtype, vl, vlenb).

GPU

GPU RV64XUn gruppo di lavoro propone in gennaio 2021un'estensione GPU denominata RV64X basata in particolare sull'estensione del processore vettoriale e sul formato VBlock proposto dal progetto GPU Libre che può essere implementato in ASIC o FPGA. La prima versione mira a utilizzare un driver compatibile con l'API Khronos Vulkan , per supportare in seguito OpenGL e Direct3D . Dovrebbe anche riguardare inizialmente il campo dell'on-board. I vincoli impostati sono:

- istruzione a 64 bit;

- Supporto di funzioni complesse sin , cos , atan , pow , exp , log , rcp, rsq, sqrt , ecc.

- Di vettori che trasportano 2-4 elementi a 8, 16 o 32 bit;

- Di matrici quadrate 2 × 2, 3 × 3 e 4 × 4;

- pixel nei formati a 8, 16, 32 e 64 bit;

- I punti in 4 dimensioni XYZW, 64 o 128 bit;

- I pixel 4 componenti RVGA, con 8, 16, 24 o 32 bit per componente;

- I texel hanno componenti UVW 3, 8 o 16 bit;

- Supporto per variabili leggere, Ia, ka, Id, kd, Is, ks...

Nel dicembre 2019, l'azienda Think Sillicon ha proposto una GPU basata sull'architettura RISC-V.

Un'altra GPU basata su RISC-V, interrottaNel 2018, il progetto Kazan o Libre RISC-V mirava a sviluppare una GPU basata su RISC-V. Nel 2020, a causa di vari disaccordi con il funzionamento della fondazione RISC-V, gli autori del progetto si riorientano verso un'architettura OpenPower, versione aperta di Power , l'architettura RISC degli anni '90 di IBM , Gli autori accendono finalmente la creazione di un'estensione del processore vettoriale denominata SV per l'architettura Power, vicina all'estensione V di RISC-V, piuttosto che lo sviluppo di una GPU.

Supporto software

Viene proposta una serie di tool gratuiti per lo sviluppo su questa architettura, tra cui la compatibilità dei compilatori GCC e LLVM (quindi Clang ), il supporto del debugger GDB , nonché dell'hypervisor ed emulatore QEMU . Il linguaggio Rust supporta RISC-V da alloranovembre 2017.

A livello di assembler , GNU Assembler supporta architetture RISC-V a 32 e 64 bit (assembler, disassembler) e riscv-assembler è un assembler in Python .

Bronzebeard è un assembler RV32IMAC scritto in Python binder assemblato in una libreria minimalista per fornire un sistema di bare metal (In) . È stato testato per la prima volta su schede di Sipeed, Longan Nano e Wio Lite e sul loro processore GigaDevice GD32V a causa della possibilità di accedere facilmente a questo tipo di materiale con il suo schermo per meno di 10 €. L'autore prevede di portarlo anche su HiFive1 Rev B. Lo stesso autore ha anche prodotto un interprete Forth bare metal per RISC-V.

Questa architettura è supportata in gennaio 2016dal kernel Linux tramite una serie di patch e da FreeBSD. La sua integrazione nel core stabile di Linux è efficace dalla versione 4.15, con un supporto più ampio dalla versione 4.17.

Il linguaggio di scripting MicroPython , una versione adattata ai microcontrollori Python , è stato portato nel 2017 da Microsemi sull'architettura RISC-V.

Arduino funziona su microcontrollori GD32V di GigaDevice . Può utilizzare il sistema in tempo reale RT-Thread e l' interfaccia grafica RTT-GUI di Arduino per questo.

Il sistema real-time Zephyr funziona anche su processori RISC-V, in particolare sulla sua emulazione da parte di Qemu e su varie implementazioni hardware.

La versione minima di Rust per embedded (Minimum Supported Rust Version (MSRV)) viene portata su RISC-V, dalla community di rust-embedded. Il sistema RustOS , basato su un kernel rCore, una versione Rust di uCore OS Plus, gira sull'implementazione Qemu di RISC-V e sui sistemi HiFive Unleashed, e viene utilizzato alla Tsinghua University per le lezioni sul sistema operativo.

La società UltraSOC sviluppa "Tessent Embedded Analytics" una soluzione di analisi e tracciamento su RISC-V, per soluzioni proprietarie o aperte. È stata acquistata dal gruppo Siemens e continua questa attività all'interno del gruppo.

Questa architettura è supportata dai sistemi operativi per Internet of Things , LiteOS (licenza BSD) e per piattaforme mobili HarmonyOS di Huawei .

Il software per aiutare a scoprire le vulnerabilità di sicurezza, al fine di essere in grado di sfruttarle, del l' Stati Uniti servizio di intelligence , NSA , Ghidra , supporta il formato binario di questa architettura.

Nel gennaio 2020Alibaba sta dimostrando Android 10 portato da T-Head sul suo SoC ICE EVB con 2 core RISC-V XuanTie C910 a 64 bit, un core vettoriale XuanTie C910V e una GPU GC8000UL Live .

Sistemi operativi per server e desktop

Sono disponibili diverse distribuzioni Linux, tra cui Debian Bullseye con oltre il 95% di pacchetti portati, Fedora , Ubuntu , Yocto . Anche i sistemi operativi FreeBSD e Haiku si avviano su RISC-V.

Linux e Haiku possono beneficiare dell'accelerazione delle schede grafiche AMD Radeon HD tramite il driver Mesa gratuito che è indipendente dall'architettura del processore.

Emulatori software

È possibile simulare queste architetture tramite diversi emulatori e hypervisor.

L'hypervisor QEMU , oltre che da ANGEL (un simulatore RISC-V in HTML5 e JavaScript ) o tramite schede ZedBoard e Zybo con FPGA Xilinx Zynq. L'emulazione RISC-V (32 e 64 bit) è supportata nativamente in Qemu dalla versione 2.12.0 rilasciata il24 aprile 2018. La versione 5.1 aggiunge il supporto per la scelta del bios negli argomenti.

TinyEMU di Fabrice Bellard (autore anche di QEMU e ffmpeg ) è un leggero emulatore RISC-V, viene utilizzato per il port di Haiku (remake gratuito di BeOS ). Viene anche utilizzato in BareDoom, un port di Doom su RISC-V tramite Barebox , questa versione di TinyEMU stessa viene ricompilata in WebAssembly (WASM) per essere eseguita in un browser.

Juice-VM è un emulatore di macchina virtuale RISC-V RV64IMASU minimalista, che supporta MMU e UART I/O. Consente di eseguire FreeRTOS e inoltre, su sistemi con risorse molto limitate, come i microcontrollori dual-core ESP32 di tipo Xtensa con 8 MB di PSRAM e 2 MB di flash SPI, il kernel Linux 5.0 compilato per architettura RISC-V.

RISC-V Rust è un emulatore RISC-V sviluppato in linguaggio Rust e funzionante in WebAssembly. L'obiettivo è utilizzare l'emulatore in un browser. I sistemi operativi GNU / Linux e xv6 -riscv funzionano su di esso.

Implementazioni hardware

strumenti di sviluppo

Wrap-V è un generatore di core RISC-V, che supporta anche l' architettura MIPS in TL-Verilog (Transaction-Level Verilog ) e passa attraverso il processore macro M4 . Permette di sviluppare nuclei le cui condutture hanno da 1 a 7 livelli. È possibile modificare l'uscita M4 per adattarla a specifiche esigenze. È anche possibile utilizzare TL-Chisel .

Implementazioni gratuite

Il microprocessore gratuito LowRISC , è un progetto di implementazione libero e aperto di RISC-V, creato da Andrew Huang (del MIT , autore anche della piattaforma aperta Novena ), Julius Baxter (progetto OpenRISC e Cambridge University ), Michael B. Taylor ( Università of California at San Diego , UCSD Center for Dark Silicon), Dominic Rizzo ( Google ATAP (en) ), Krste Asanović ( University of California at Berkeley ).

Il NEORV32 è un'implementazione gratuita ( clausola di licenza BSD 3) di un SoC di tipo microcontrollore indipendente dalla piattaforma per FPGA scritti in VHDL. È compatibile con la specifica RISC-V 2.2 per RV32 e supera il test di conformità. FreeRTOS è stato portato su questo SoC. Si basa sul lavoro svolto dagli sviluppatori su neo430, un'implementazione di un processore di tipo micro FPGA compatibile con l' MSP430 di Texas Instruments .

Il PicoRV32 è un'implementazione gratuita, sotto licenza ISC , che supporta i set di istruzioni RV32IMC il cui obiettivo è avere il minor footprint possibile, con la scelta tra 750 e 2000 LUT e una frequenza massima da 250 a 450 MHz. Il suo scopo è quello di essere un processore ausiliario su un FPGA o ASIC. Può essere configurato come core RV32E, RV32I, RV32IC, RV32IM o RV32IMC (vedi la sezione #Nomenclatura delle estensioni ).

Western Digital offre una gamma di core chiamati SweRV, open source, disponibili tramite CHIP Alliance. Hanno anche annunciato una collaborazione con Codasip per offrire supporto commerciale a questi cuori. Questi processori ad alte prestazioni sono destinati a domini embedded e supportano il set di istruzioni RV32IMC. La famiglia SweRV è così suddivisa:

- SweRV EH1 Superscalar Core ha 2 code di esecuzione e si basa su una pipeline a 9 fasi.

- Il core superscalare multi-thread SweRV EH2 può gestire 2 thread contemporaneamente con 9 fasi della pipeline.

- Il nucleo SweRV EL2 a uscita singola con 4 stadi di tubazione.

L' Accademia cinese delle scienze ha rilasciato il processore Xiangshan , sotto licenza gratuita ( licenza Mulan v2 , approvato OSI ) su11 giugno 2021su Github . Il processore è sviluppato in linguaggio Chisel , che secondo gli sviluppatori ha 5 volte meno righe di codice rispetto a Verilog e permette uno sviluppo più veloce. Al momento del suo rilascio, il processore supporta la distribuzione Debian Bulleseye per RISC-V. Una prima implementazione hardware esce inluglio 2021, chiamato Yanqihu, inciso in 28nm e frequenza tra 1.2 e 1.3 GHz, ha prestazioni per GHz simili all'ARM Cortex-A72 con CPU 7/Ghz SPEC 2006. Una seconda versione prevista per l'autunno dello stesso anno chiamata Nanhu, incisa in 14nm e operando a 2 GHz, dovrebbe raggiungere prestazioni per GHz simili ad un Intel i9-10900K (11.08/Ghz) con 10/Ghz SPEC CPU 2006, e una potenza di calcolo, a questa frequenza, paragonabile a quella di un ARM Cortex- A76 .

Implementazioni RISC-V proprietarie

SiFive, annuncia una startup in luglio 2016Il SiFive U5 Coreplex , usando un'architettura RISC-V e per impiantare U54 fino a otto core per SoC , ciascuna comprendente cache istruzioni e dati di 1 ° livello, il SoC include una grande cache di 2 e livello. L'obiettivo sarà quello di implementare prima versioni per hardware molto specifico che non necessita di molta potenza, ma all'inizio funzioni specializzate, per poter poi migliorare le tecnologie.

Nel 2018 la startup SiFive, creata dagli sviluppatori di RISC-V, ha presentato al FOSDEM la scheda HiFive Unleashed , composta da un processore SoC SiFive Freedom U540 (4 + 1 core RISC-V fino a 1,5 GHz) e 8 Gio di RAM ECC, Porta ethernet Gb e in grado di eseguire GNU/Linux .

Shakti è un'iniziativa indiana di progetti di diversi processori basati sull'architettura RISC-V e suddivisi in 6 serie: E-class per embedded, C-Class per microcontrollori, I-Class per microprocessori per thin client, M-Class per office automation , S-Class per workstation e server e infine H-Class per supercomputer.

Codasip è la prima azienda ad aver sviluppato un core compatibile RISC-V non libero in gennaio 2016(Codix) e ha continuato la sua offerta con famiglie di core per embedded e aree applicative. I core sviluppati da Codasip sono scritti in CodAL, un linguaggio di descrizione dell'architettura. Lo strumento Studio viene utilizzato per ottenere i simulatori e i file necessari per l'implementazione fisica di questi core.

La famiglia L riunisce core a 32 bit a bassa potenza, mirati ai domini di bordo, offrendo un'unità di calcolo in virgola mobile opzionale. Questa famiglia è disponibile in 3 o 5 fasi di pipeline.

La famiglia H riunisce core a 64 bit ad alte prestazioni destinati a domini integrati e offre un'unità di calcolo mobile come opzione.

La famiglia A è costituita da core a 64 bit in grado di eseguire Linux, con la possibilità di estenderli con l'estensione "P". Questi core hanno 7 fasi di pipeline, un'unità di calcolo mobile, una MMU. Inoltre, le versioni -MP integrano cache di livello 1 (L1) e 2 (L2) e supportano fino a 4 core per cluster.

Il core uRISC-V reso disponibile in Codasip Studio è destinato all'apprendimento o al test.

Embedded e microcontrollori

Al 7 ° RISC-V Workshop , Western Digital ha annunciato che l'azienda avrebbe sviluppato processori RISC-V. L'obiettivo di Western Digital è iniziare una transizione verso soluzioni open source per i suoi server di storage. In definitiva, WD prevede di vendere quasi due miliardi di processori RISC-V all'anno.

Nel 2018, la startup fabless GreenWave di Grenoble, ha presentato il GAP8, un processore a basso consumo per IoT, ottimizzato per l'intelligenza artificiale .

Nel 2019, GigaDevice Semiconductor lancia la serie di microcontrollori GD32V , basata sulla versione a 32 bit dell'architettura. Tra le 14 versioni, il GD32VF103 ha un clock a 108 MHz e accede alla sua memoria flash integrata senza stati di attesa (in) , quindi senza latenza. Dispone di 128 KiB di memoria flash su chip e 32 KiB di SRAM , 2 convertitori analogico-digitale a 12 bit e 2 convertitori digitale-analogico a 12 bit, nonché varie interfacce di comunicazione (3 SPI, 2 I2C , 3 USART, 2 UART, 2 I2S, 2 CAN e 1 USB OTG). Il chip è compatibile pin-to-pin con i suoi microcontrollori GD32 basati sull'architettura ARM , così come STM32 di STMicroelectronics , rendendo facile il porting di applicazioni da un'architettura all'altra e anche compatibile con Arduino . I GD32V sono utilizzati in particolare nella scheda di sviluppo Sipeed Longan Nano .

Sipeed ha anche sviluppato la scheda Sipeed M1 (o Kendryte KD233), dotata di un SoC Kendryte K210 composto da 2 core RISC-V a 64 bit e un processore di intelligenza artificiale. Queste schede sono progettate per funzionare con FreeRTOS . Questa scheda utilizza MAIXPy, una versione adatta di MicroPython, programmabile tramite Plateform.IO. Esistono diverse varianti, come MaixDuino , la cui scheda ha un formato compatibile con Arduino e supporta l'IDE. È anche possibile utilizzarlo con un sistema operativo Linux . Sono disponibili altre versioni più compatte. Nelluglio 2021 Canaan ha rilasciato il Kendryte K510, una versione migliorata comprendente una parte di microprocessore composta da 2 core RV64 e un acceleratore composto da un altro RV64 con estensione DSP.

Nel 2019, il presidente degli Stati Uniti, Donald Trump, minaccia di bloccare i fornitori di Huawei, tra cui fondatori come TMSC, e la società britannica ARM, che fino ad allora forniva l'IP dei core utilizzati nei processori HiSilicon di Huawei. L'azienda americana Nvidia dopo aver acquistato i diritti della società ARM dalla giapponese SoftBank , Huawei ha dovuto trovare una soluzione alternativa e sembra essersi rivolta a RISC-V. I primi kit di sviluppo HiHope HiSpark Wifi IoT utilizzano un microcontrollore Hisilicon Hi3518, compatibile con le sue nuove piattaforme, Huawei LiteOS e HarmonyOS . I compilatori forniti con sono compilatori GCC destinati a codici di architettura RISC-V a 32 bit.

Nel luglio 2021, Espressif annuncia la disponibilità di un nuovo modello NodeMCU basato sul processore ESP32-C3 , architettura RISC-V.

Moduli di reteOpenWifi , presentato indicembre 2019, è uno stack WiFi open source compatibile con Linux che può essere eseguito su FPGA, è stata eseguita un'implementazione funzionale su Xilinx FPGA, collegato alla scheda RF fmcomms2 / fmcomms4

I moduli BL602 / BL604 di Bouffalo Lab, basati su RISC-V a 32 bit, sono moduli WiFi e Bluetooth 5.0 LE. Sipeed e Pine64 dovrebbero integrarli nelle loro mappe per IoT.

Nel novembre 2020, Espressif annuncia il rilascio di ESP32-C3, WiFi e BLE , un processore in linea con ESP32 , ma compatibile pin-to-pin con ESP8266 e che utilizza l'architettura RISC-V a 32 bit invece di Xtensa LX6 . Ha un processore crittografico, ma nessun DSP a differenza di ESP32.

SpazioL' agenzia spaziale europea sta sviluppando un processore neurale chiamato " NOEL-V " e basato sull'ISA RISC-V e sulla sua estensione vettoriale (V o RVVE) utilizzando la tecnologia RHBD (Radiation Hardened By Design), per i vincoli dell'ambiente spaziale ( temperatura e raggi ionizzanti), così come i vincoli di efficienza energetica, al centro dei satelliti. Il progetto è guidato da Cobham Gaisler, presso il Centro europeo di ricerca e tecnologia spaziale (ESTEC), che aveva già prodotto nel 2019, un processore simile chiamato " LEON " basato sull'architettura SPARC -V8 alla fine degli anni '90.

VariePinecil di Pine64 è un saldatore regolato elettronicamente basato su un processore " Bumblebee Core " RISC-V RV32IMAC da 108 MHz.

Sipeed RV-Debugger Plus è un connettore UART open source (seriale) e debugger JTAG , basato sul SoC Bouffalo Lab BL702, che utilizza un microcontrollore RISC-V a 32 bit, 144 Mhz, comprendente una FPU, un modulo di crittografia, Audio (I2S master/slave), gestisce Zigbee 6, Bluetooth 5.0 LE, WiFi e internet. Il firmware è un software libero , è possibile utilizzarlo anche come scheda di sviluppo.

FPGA

ZedBoard e Zybo con FPGA Xilinx .

La mappa materiale gratuita , LicheeTang, di LicheePi, presentata insettembre 2018, scheda che utilizza un microcontrollore basato sull'architettura RISC-V e utilizza un FPGA, utilizza un Anlogic EG4S20. Dispone di GPIO per poter collegare diversi tipi di elementi elettronici.

La scheda Tang Nano FPGA , presentata inottobre 2019, di Sipeed, utilizza un FPGA GOWIN Semi GW1N della sua famiglia LittleBee .

La serie core del processore Hummingbird E200 (o HBird E200) è un'implementazione cinese open source di RISC-V e include implementazioni FPGA .

Nel dicembre 2019, viene presentato OpenWiFi. È uno stack WiFi hardware e software gratuito in esecuzione su FPGA, con un'implementazione su Xilinx.

Nel giugno 2020, Efinix offre 3 architetture RISCV32I a 32 bit ottimizzate per l'FPGA Trion

Nel luglio 2020, viene presentata la scheda SAVVY-V open source basata sul SOC PolarFire a 64 bit. Il PolarFire SoC Icicle utilizza un SoC FPGA con 5 core a 64 bit, tra cui un RV64IMAC e quattro RV64GC e dotato di 2 GiB di RAM LPDDR4, presentato per la prima volta indicembre 2019Ha finalmente rilasciato il 3 ° semestre 2020. PolarBerry viene proposta anche la variante di crawdfundingottobre 2020.

SBC

Diverse schede di tipo SBC, e con Linux, sono presentate dal 2018, cercando di fissare un prezzo simile al popolare Raspberry Pi : L'SBC HiFive Unleashed (en) è presentato infebbraio 2018, basato su un SoC composto da quattro core U54 RV64GC (64 bit) da 1,5 GHz e 8 GiB di RAM ECC di tipo DDR4 , su base crowdfunding .

Imagination Technologies e il RISC-V Internazionale Open Source di laboratorio (Rios) si sono uniti per fare un SBC- carta di tipo chiamato PicoRio , svelato insettembre 2020al RISC-V Global Forum , la piattaforma è generalmente open source, ad eccezione di alcune parti essenziali come l'I/O o l'accesso alla memoria.

Nel novembre 2020, Sipeed annuncia un SBC utilizzando un SoC AllWinner , single-core , composto da un XuanTie C906 (RV64GCV) a 1 GHz in 22 nm, realizzato dai progettisti del processore RISC-V a 64 bit a 16 core, XT910 di Alibaba, non ha una GPU 3D, ma una GPU 2D e un decodificatore video hardware, H.264 e H.265, da 64 MiB a 256 MiB di RAM saldata (e alcuni modelli potrebbero avere RAM esterna), oltre a HDMI, Connessioni Gb ethernet, USB e USB OTG

Nel gennaio 2021, L'SBC utilizza un SoC BeagleV StarFive JH7100 comprendente un processore RISC-V double heart SiFive U74, un DSP DSP Vision Tensilica-VP6, un motore NVDLA (open architecture NVIDIA Deep Learning Accelerator) e un motore di rete neurale per l'accelerazione dell'IA. La sua prima versione non ha un processore geometrico 3D, la seconda versione avrà una GPU di Imagination Technologies (quindi senza un driver aperto). Infine, il SoC include una VPU, in grado di decodificare H.264 e H.265 fino a 4Kp60, o due flussi in 2Kp30. La scheda è dotata di 4 o 8 GB di RAM in LPDDR4, 4 porte USB 3.0, una porta ethernet da 10Gb, HDMI 2.0, DSI, due ISP, una porta a 40 pin e alimentata da USB-C. Sono disponibili due versioni, una con 4 GB di RAM a $ 100 e una con 8 GB a $ 150, i processori incisi a 7 nm da TSMC, girano a 3.5 GHz, sono di tipo RV64GCVBH (con in particolare un'unità vettoriale) e un processore raggiunge prestazioni con ARM Cortex-A76 e A77 . Nelmaggio 2021, la distribuzione Fedora viene proposta come distribuzione predefinita, con le prime mappe a disposizione degli sviluppatori. XFCE è il gestore di finestre predefinito, che può essere visualizzato sull'uscita HDMI.

Nel Febbraio 2021, Pine64 , annuncia il rilascio di un SBC di sviluppo, basato su un SoC comprendente un core RV64GCV (XuanTie C906) e un secondo RISC-V BL602 a 32 bit ( ESP32-C ), per la parte di rete wireless, driver aperti in fase di sviluppo per questo uno. L'obiettivo è quello di fissare un prezzo inferiore a $ 15 (US), in modo da rendere la piattaforma di sviluppo accessibile al maggior numero di persone possibile.

Il computer portatile

L' Accademia cinese delle scienze ha annunciato ingiugno 2021, che sta preparando il rilascio di 2.000 laptop basati su RV64GC entro la fine del 2022 e per questo lavoro sull'ottimizzazione per RISC-V dei motori Firefox ( spiderMonkey e il suo compilatore al volo (JIT)) e Chrome / Chromium ( WebKit ) in modo che funzionino correttamente lì.

Server

Il gruppo Alibaba ha progettato lo XuanTie 910 (o XT910), un SoC per server , composto da 16 core RISC-V RV64GCV a 64 bit, organizzati in cluster di 4 core con 32 o 64 kb di cache dati e altrettanti in cache. istruzione. Il gruppo afferma che le prestazioni di un core sono dello stesso ordine di quelle di un ARM Cortex-A73 .

Supercomputer

L' Unione Europea ha lanciato un progetto di supercomputer basato sull'architettura RISC-V, chiamato European Processor Initiative (EPI), finanziato dal programma EU Horizon 2020, sviluppato da 26 partner (tra cui la Fondazione RISC-V, il Centro Nacional de Supercomputación (CNS o BSC), CEA , Infineon o anche STMicroelectronics ) da 10 paesi. Un SoC che utilizza l'architettura RISC-V per acceleratori sviluppato anche in Europa, mira a produrre un supercomputer esascala, oltre che a fornire in campo automobilistico , basato su tecnologie europee. L'utilizzo dell'architettura ARM come processore principale è previsto ma non certo, in questo caso RISC-V sarebbe limitato agli acceleratori di calcolo. Il progetto cerca di riutilizzare i sistemi esistenti (già implementati sotto GNU/Linux ).

Appendici

Note e riferimenti

- (in) " RISC-V: An Open Standard for SoCs " , EE Times (consultato il 17 agosto 2014 )

- (en) Lucian Armasu, "I grandi giocatori della tecnologia iniziano ad adottare l'architettura del chip RISC-V " , su Tom's Hardware ,29 novembre 2017

- (en) Lucian Armasu, " Nvidia Job Listings Point to Ambicious RISC-V Plans " , su Tom's Hardware ,10 ottobre 2019

- (in) William G. Wong, " The Rise of RISC-V on Display at Workshop " , su ElectronicDesign ,5 dicembre 2017

- (in) Chris Williams, " In braccio! Arm uccide il suo sito diffamatorio anti-RISC-V dopo la rivolta del proprio personale " , su The Register ,10 luglio 2018

- (in) Joel Hruska, " ARM RISC-V uccide il suo sito web dopo la rivolta del personale FUD " su ExtremeTech ,12 luglio 2018

- (in) Nathaniel Mott, " TSMC non vuole produrre i suoi chip negli Stati Uniti " , su Tom's Hardware ,1 ° novembre 2019

- (en) Nathaniel Mott, " Rapporto: RISC-V prevede di trasferirsi dagli Stati Uniti alla Svizzera " , su Tom's Hardware ,26 novembre 2019

- " RISC V si trasferisce in Svizzera per sfuggire alla guerra commerciale sino-americana " , su 01Net

- (en) Jean-Luc Aufranc, " La scheda di sviluppo HiSpark WiFi IoT basata su Hi3861 supporta LiteOS e HarmonyOS " , su software CNX ,12 ottobre 2020

- (in) Gareth Halfacree, " René Rebe patch il kernel Linux per" Il primo al mondo "Guarda una Radeon 6700XT era RX RISC-V PC " su hackster.io ,21 luglio 2021

- (in) " BOOM RISC-V Core open source viene eseguito su istanze Amazon EC2 F1 " su software CNX ,13 dicembre 2018

- (en) Jean-Luc Aufranc, “ Spiegazione delle basi e delle estensioni RISC-V ” , su CNX-Software ,27 agosto 2019

- Waterman e Asanović 2019 , p. 35.

- Jim Ledin, " The RISC-V Architecture " , su DZone ,5 giugno 2020

- (in) Andrew Waterman e Krste Asanović The RISC-V Instruction Set ManualVolume I: User-Level ISA Document Version 2.2 , CS Division, EECS Department, University of California, Berkeley,2017( leggi in linea ) , p. 27

- (en) cap. 5 "RV64I Base Integer Instruction Set, Version 2.1" , in RISC-V Instruction Set Manual, Volume I: RISC-V User-Level ISA, 20191214- December 2019 ,dicembre 2019( leggi in linea )

- (a) RISC-V "V" Vector Extension ( leggere online )

- (in) Jon Peddie, " RV64X: una GPU gratuita e open source per RISC-V " su EE Times ,27 gennaio 2021

- (it) Jean-Luc Aufranc, " Think Silicon NEOX | V è la prima GPU basata su RISC-V ISA " su CNX-Software ,4 dicembre 2019

- (in) " Kazan " su salsa.debian.org

- (in) " Download - RISC-V " su riscv.org accessdate = 17 agosto 2014

- Alicia Daleiden, " Rust Comes to RISC-V " , su Riscv.org ,28 novembre 2017

- Andrew Back, " Rust Comes to RISC-V " , su ABopen ,28 novembre 2017

- https://bronzebeard.readthedocs.io/en/latest/

- (in) " Ecosistema minimo per lo sviluppo RISC-V bare-metal in python " su Python Awesome.com ,29 giugno 2021

- https://github.com/theandrew168/derzforth

- " [base] Revisione 295041 " , su svnweb.freebsd.org (consultato il 29 gennaio 2016 )

- " Anteprima poster RISC-V - 7° Workshop RISC-V " ,28 novembre 2017(consultato il 17 dicembre 2018 )

- (a) " Gd32v " su Arduinolibraries.info

- (in) " Zephyr " sulla guida introduttiva a RISC-V (su readthedocs.io)

- (in) " Versione minima supportata Rust (MSRV) " su Comtpe Rust integrato su Github

- (in) oscourse-Tsinghua su Github, " RCORE "

- (in) " RISC-V è un'architettura di set di istruzioni open source che apre la strada ai prossimi 50 anni di innovazione e progettazione informatica. » , Su tessentembdedanalytics.com

- (in) " Ghidra Software Reverse Engineering Framework " su Github

- (in) " " ghidra / Ghidra / Processors at Ghidra_9.2_build " " sulla fonte del codice Ghidra su Github ,13 novembre 2020(consultato il 21 novembre 2020 )

- (it) Jean-Luc Aufranc, " Android 10 portato su scheda RISC-V con processore Alibaba T-Head XuanTie C910 " su software CNX ,22 gennaio 2021

- (in) " RISC-V " su Debian .org

- https://fedoraproject.org/wiki/Architectures/RISC-V

- (it) " Rilasciato Ubuntu 20.04 / 21.04 64-bit RISC-V per QEMU, schede HiFive " su CNX Software ,28 giugno 2021

- https://github.com/riscv/meta-riscv

- https://wiki.freebsd.org/riscv

- https://discuss.haiku-os.org/t/my-haiku-risc-v-port-progress/10663

- https://discuss.haiku-os.org/t/my-progress-on-real-risc-v-hardware/10963/30

- https://www.youtube.com/watch?v=wHp-UIGov8c

- (a) " Guida introduttiva di RISC-V " sul riscv.org (accessibile 17 agosto 2014 ) , archivio

- (in) " riscv-tools " su riscv.org (consultato l' 11 luglio 2016 )

- (in) " ChangeLog / 2.12 - RISC-V " su qemu

- (in) " QEMU System Emulation User's Guide " , qemu (consultato il 31 gennaio 2021 )

- (in) "I miei progressi nel porto di Haiku RISC-V " su Haiku-os.org

- (in) A3F, " bareDOOM " su BareDoom su Github

- (in) " JuiceVm " sull'account juiceRv su Github

- (in) " Linux 5.0 viene mostrato per avviare il processore ESP32 " su CNX-Software ,18 luglio 2021

- (in) " riscv-rust " su Github

- Abhishek Jadhav, " WARP-V: un generatore di core CPU RISC-V che supporta MIPS ISA " , su CNX-Software

- " Il processore RISC-V NEORV32 "

- (in) " Il processore NEORV32 (RISC-V) " su OpenCores.org

- " Il processore NEO430 " , su Github

- (in) Gareth Halfacree, " I progettisti di chip cinesi sperano di rovesciare il Cortex-A76 di Arm con il design Xiangshan RISC-V Con licenza permissiva, la seconda iterazione del processore mira a 2GHz a 14nm " , su The Register ,6 luglio 2021

- (in) " PicoRV32 - A RISC-CPU V ottimizzato per dimensioni " su GitHub

- " Codasip facilita le implementazioni hardware dell'open source RISC-V SweRV Core di Western Digital " , su www.lembarque.com ( consultato il 20 maggio 2021 )

- " Codasip estende il supporto per i core Western Digital RISC-V SweRV ai modelli incorporati " , su www.lembarque.com ( consultato il 20 maggio 2021 )

- " OpenXiangShan / XiangShan " , sull'account OpenXiangShan su Github

- (zh)包云岗, “ 首届RISC-V中国峰会2021年6月21日起在上海举行,有什么值得关注的 地方? ” , Su知乎

- (en) Jean-Luc Aufranc, " Processore RISC-V a 64 bit open source XiangShan per rivaleggiare con Arm Cortex-A76 " , su CNX-Software ,5 luglio 2021

- (in) " Accademia cinese delle scienze ha rilasciato il processore RISC-V domestico" Xiangshan "qui HA eseguito con successo Linux e sarà rilasciato a luglio " su min.news ,2 luglio 2021

- (in) Nicole Hemsoth, " L' avvio si prende un rischio è RISC-V Custom Silicon " , su The Next Platform ,11 luglio 2016

- Alasdair Allan, “ Risc-V sta finalmente decollando? » , Su Hacksters.io ,19 febbraio 2018

- (in) " Processori " su shakti.org.in

- (in) " Codasip entra a far parte della RISC-V Foundation e annuncia la disponibilità dell'IP del processore conforme a RISC-V Codix " su progettazione e riutilizzo (consultato il 20 maggio 2021 )

- " Codasip lancia 3 processori RISC-V multi-core per IA Edge " , su Electronics-ECI ,8 dicembre 2020(consultato il 20 maggio 2021 )

- " Codasip offre la possibilità di esercitarsi su una reale implementazione di un processore RISC-V " , su www.lembarque.com (visitato il 20 maggio 2021 )

- (it) Jean-Luc Aufranc, " GreenWaves GAP8 è un processore IoT RISC-V a bassa potenza ottimizzato per applicazioni di intelligenza artificiale " su CNX-Software , 27febbraio 2018

- (it) GigaDevice Semiconductor Inc, Manuale utente GD32VF103 ,ottobre 2019, 533 pag. ( leggi in linea )

- Gerhard Steizer, " RISC-V per tutti " , su Elektronknet.de ,4 settembre 2019

- (it) Jean-Luc Aufranc, " GigaDevice GD32 è un MCU Cortex M3 STM32 più veloce, compatibile con software e pin-to-pin " su CNX-Software ,21 dicembre 2015

- (in) Brian Benchoff, " Nuova parte: il chip RISC-V con reti neurali integrate " su Hack a Day ,8 ottobre 2018

- Kadionik Patrice, " Maixduino: Do AI on a RISC-V Processor ", Hackable , n o 36 mesi = gennaio,2021( leggi in linea )

- (in) "Il processore AI tri-core RISC-V Kendryte K510 offre fino a 3 TOPS " sul software CNX ,9 luglio 2021

- (it) Jean-Luc AUFRANC, " Le schede NodeMCU ESP32-C3 WiFi e BLE IoT si presentano per circa $ 4 " su CNX-Software ,12 luglio 2021

- (en) Jean-Luc Aufranc, " Lo stack WiFi compatibile con OpenWiFi Open-Source Linux gira su hardware FPGA " , su CNX-Software ,16 dicembre 2019

- (it) Jean-Luc Aufranc, " BL602 / BL604 RISC-V WiFi e Bluetooth 5.0 LE SoC venderanno a prezzi ESP8266 " su CNX-Software

- (it) Jean-Luc Aufranc, "Il processore ESP32-C3 WiFi e BLE RISC-V è pin-to-pin compatibile con ESP8266 " su CNX-Software ,22 novembre 2020

- (in) Gareth Halfacree, " Reti neurali profonde ... IN SPAAACE: i chip RISC-V potenziati dal vettore potrebbero fornire satelliti a bordo " , su The Register ,1 ° luglio 2021

- Di Mascio & Al 2021 .

- (in) Gareth Halfacree, " Pine apre gli ordini per il suo saldatore Pinecil Smart con alimentazione RISC-V - con scheda breakout gratuita " su Hackster.io ,25 novembre 2020

- (it) Jean-Luc Aufranc, " $ 3.5 RV-Debugger Altro debug JTAG UART e scheda vengono forniti con BL702 BLE e Zigbee SoC RISC-V " su CNX-Software ,21 giugno 2021

- (in) " La scheda FPGA LicheeTang Anlogic EG4S20 si rivolge allo sviluppo RISC-V " sul software CNX ,4 settembre 2018

- "La scheda FPGA Tang Nano da $ 5 presenta GOWIN GW1N" LittleBee "FPGA " , sul software CNX ,15 ottobre 2019

- (en + zh) " Hummingbird E200 Opensource Processor Core " , su GitHub

- (it) Jean-Luc Aufranc, " Efinix rilascia tre SoC definiti dal software RISC-V ottimizzati per Trion di FPGA " su Cnt-Software ,6 giugno 2020

- (it) Jean-Luc Aufranc, " PolarBerry è un modulo FPGA RISC-V compatto compatibile con Linux e SBC (Crowdfunding " su CNX Software ,5 luglio 2020

- (it) Jean-Luc Aufranc, " La prossima scheda cluster RISC-V open source SAVVY-V supporta 10GbE tramite Microsemi PolarFire 64-bit RISC-V SoC " su software CNX ,20 luglio 2020

- (it) Jean-Luc Aufranc, " PolarBerry è un modulo FPGA RISC-V compatto compatibile con Linux e SBC (Crowdfunding " su CNX Software ,30 ottobre 2020

- (it) Jean-Luc Aufranc, " SiFive introduce HiFive Unleashed RISC-V Linux Development Board (Crowdfunding) " su CNX Software ,4 febbraio 2018

- (it) Jean-Luc Aufranc, " PicoRio Linux RISC-V SBC è un'alternativa open source alla scheda Raspberry Pi " su CNX-Software ,4 settembre 2020

- Jean-Luc Aufranc, " processore Allwinner RISC-V basato su XuanTie C906 per alimentare $ 12 + Linux SBC " , su software CNX ,9 novembre 2020

- Jean-Luc Aufranc, " $ 119 + BeagleV potente, open-hardware RISC-V Linux SBC mira ad applicazioni AI " , su CNX-Software ,13 gennaio 2021

- (in) Chloe Ma, " RISC-V Star Rising from the East - Introducing StarFive " su riscv.org ,1 ° marzo 2021

- (zh) " 重磅 " , sull'account Starfive su Weixin ,10 dicembre 2020

- (in) Starfive Tech, " BeagleV Starlight RISC-V Fedora picture " su Gihtub

- (in) PINE64, " Aggiornamento di febbraio: mostra e racconta " su Pine64.org

- (in) Gareth Halfacree, " ISCAS cinese costruirà 2.000 laptop RISC-V entro la fine del 2022 mentre la nazione cerca di ridurre la dipendenza da Arm, chip Intel " , su The Register ,8 giugno 2021.

- (it) Jean-Luc Aufranc, " Maggiori dettagli su Alibaba XT910 64-bit RISC-V Core " sul software CNX ,25 agosto 2020

- (in) " Come la leva del processore dell'iniziativa europea è RISC-V per il futuro del supercalcolo " su Inside HPC ,22 agosto 2019

Bibliografia in linea

-

(it) “ Specifiche ” , su riscv.org

- (it) Andrew Waterman e Krste Asanović, The RISC-V Instruction Set Manual - Volume I: Unprivileged ISA , CS Division, EECS Department, University of California, Berkeley,dicembre 2019( leggi in linea )

- (it) Andrew Waterman e Krste Asanović, The RISC-V Instruction Set Manual - Volume II: Privileged Architecture , CS Division, EECS Department, University of California, Berkeley,giugno 2019( leggi in linea )

- (it) Krste Asanović (en) e David Patterson , I set di istruzioni dovrebbero essere gratuiti: il caso di RISC-V , Ingegneria elettrica e informatica Università della California a Berkeley,agosto 2014( presentazione online , leggi online )

- (Deprecato) Il set di istruzioni RISC-V HotChips 25 (2013)

- L'ecosistema software RISC-V HPCA 2015, Tutorial

- Yunsup Lee, generatore di SoC "Rocket Chip" RISC-V a Chisel , UC Berkeley, HPCA,2015( leggi in linea )

- (it) d0iasm, Scrivere un emulatore RISC-V in Rust ( leggi online )( fonte )

- (it) Hiroaki Kaneko et Akinori Kanasugi, Un monitor di codice macchina integrato per un processore RISC-V su un FPGA , SpringerLink,2020( ISSN 1614-7456 , OCLC 1196515116 )

- (it) Johannes Geier, Framework di iniezione di guasti basato su RTL rapido per core RISC-V , Monaco di Baviera, Masterarbeit Technische Universität,2020( OCLC 1193312286 )

- (it) SHAKTI Development Team, RISC-V Assembly Language: Programmer Manual Part I , Madras, SHAKTI Development Team,2020( leggi in linea )

- (it) Stefano Di Mascio, Alessandra Menicucci, Eberhard Gill, Gianluca Furano e Claudio Monteleone, “ Processo decisionale a bordo nello spazio con reti neurali profonde e processori vettoriali RISC-V ” , Journal of Aerospace Information Systems ,giugno 2021( DOI 10.2514 / 1.I010916 , presentazione online , leggi online )

Bibliografia su carta

Lavori- (it) Andrew Shell Waterman, Progettazione dell'architettura del set di istruzioni RISC-V , Berkeley, CA,2016( OCLC 957714390 ) (tesi di dottorato in Computer Science University of California, Berkeley 2016)

- (it) John L. Hennessy e David A. Patterson, Computer Organization and Design RISC-V Edition , Morgan Kaufmann,aprile 2017, 696 pag. ( ISBN 978-0-12-812275-4 , e-ISSN 978-0-12-812276-1 [controllare: ISSN non valido ] )

- (zh-Hans)胡振波,手把手教 你 设计 CPU : RISC-V 处理器 篇, 北京, 人民 邮电 出版社,maggio 2018, 480 pag. ( ISBN 978-7-115-48052-1 , presentazione online )

- (ja)デイビッド·パターソン(David A Patterson) eアンドリュー·ウォーターマン(Andrew Waterman) ( trans. 成田光彰(Narita)), RISC -V原典(リスクファイブ原典):オープン·アーキテクチャのススメ,日経BP2018, 224 pag. ( ISBN 978-4-822292-812 )

- Gaétan Kuetche Saadeu, Progettazione di un microcontrollore multi-core RISC-V Introduzione alla progettazione di un microcontrollore utilizzando Arduino Shields , Saarbrücken, European University Publishing,2019( ISBN 9786139502493 )

- (it) John L Hennessy e David A Patterson, Architettura del computer: un approccio quantitativo , Cambridge, Massachussetts, Elsevier, coll. "Serie Morgan Kaufmann in architettura e design dei computer",2019( ISBN 9780128119068 )

- (zh-Hans)胡振波, RISC-V 架构 与 嵌入式 开发 快速 入门, 北京, 人民 邮电 出版社,2019, 354 pag. ( ISBN 9787115494139 )

- (it) Anthony J Dos Reis, linguaggio assembly RISC-V , Stati Uniti,2019, 149 pag. ( ISBN 9781088462003 )

- (it) Jim Ledin, Modern Computer Architecture and Organization: Learn X86, ARM e RISC-V Architectures and the Design of Smartphones, PC and Cloud Servers , Birmingham, Packt Publishing,2020( ISBN 978-1-838987-107 )

- Shruthi K Muchandi, Abilitazione della co-progettazione acceleratore-SoC mediante RISC-V Chipyard , Charlotte, Università del North Carolina,2020( ISBN 9781392495506 )

- (it) Jing Chen, Accelerazione hardware per funzioni elementari e processore RISC-V , Montreal, McGill University Libraries,2020( OCLC 1199006597 )

- (it) Vladimir Herdt, Daniel Große e Rolf Drechsler, Prototipazione virtuale avanzata: con casi di studio RISC-V , Cham, Springer,2021( ISBN 978-3-030-54827-8 , DOI 10.1007 / 978-3-030-54828-5 )

- Kadionik Patrice, " Maixduino: do AI on a RISC-V processor ", Hackable , n o 36,gennaio 2021( leggi in linea )

link esterno

- http://riscv.org/ - Sito ufficiale

- http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-146.pdf - Set di istruzioni RISC-V e confronti con altre architetture simili.

- https://riscv.org/software-tools/riscv-angel/ - ANGEL, set di istruzioni RISC-V Simulatore HTTP

- (it) “ Analizzare l'architettura del set di istruzioni RISC-V ” , su Adapteva - confronto tra l'architettura RISC-V (versione a 32 bit) e l'architettura Adapteva .

- (it) " RISC-V " , su wiki.debian.org Port di Debian su RISC-V

- (it) " RISC-V Cores and SoC Overview " , su Awesome Open Source - Elenco delle implementazioni